Execution control for TM4C platform.

More...

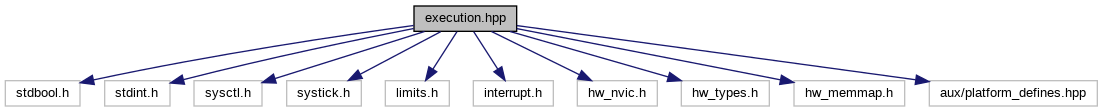

#include <stdbool.h>

#include <stdint.h>

#include <sysctl.h>

#include <systick.h>

#include <limits.h>

#include <interrupt.h>

#include <hw_nvic.h>

#include <hw_types.h>

#include <hw_memmap.h>

#include <aux/platform_defines.hpp>

|

| struct | CoreDebug_Type |

| | Structure type to access the Core Debug Register (CoreDebug). More...

|

| |

| struct | DWT_Type |

| | Structure type to access the Data Watchpoint and Trace Register (DWT). More...

|

| |

| struct | SCB_Type |

| | Structure type to access the System Control Block (SCB). More...

|

| |

Execution control for TM4C platform.

◆ __I

| #define __I volatile const |

defines 'read only' permissions

◆ __O

defines 'write only' permissions

◆ __IO

defines 'read / write' permissions

◆ __IM

| #define __IM volatile const /*! Defines 'read only' structure member permissions */ |

◆ __OM

| #define __OM volatile /*! Defines 'write only' structure member permissions */ |

◆ __IOM

| #define __IOM volatile /*! Defines 'read / write' structure member permissions */ |

◆ SCB_ICSR_VECTACTIVE_Pos

| #define SCB_ICSR_VECTACTIVE_Pos 0 |

SCB ICSR: VECTACTIVE Position

◆ SCB_ICSR_VECTACTIVE_Msk

| #define SCB_ICSR_VECTACTIVE_Msk (0x1FFUL << SCB_ICSR_VECTACTIVE_Pos) |

SCB ICSR: VECTACTIVE Mask

◆ CoreDebug_DEMCR_TRCENA_Pos

| #define CoreDebug_DEMCR_TRCENA_Pos 24U |

CoreDebug DEMCR: TRCENA Position

◆ CoreDebug_DEMCR_TRCENA_Msk

| #define CoreDebug_DEMCR_TRCENA_Msk (1UL << CoreDebug_DEMCR_TRCENA_Pos) |

CoreDebug DEMCR: TRCENA Mask

◆ DWT_CTRL_CYCCNTENA_Pos

| #define DWT_CTRL_CYCCNTENA_Pos 0U |

DWT CTRL: CYCCNTENA Position

◆ DWT_CTRL_CYCCNTENA_Msk

| #define DWT_CTRL_CYCCNTENA_Msk (0x1UL /*<< DWT_CTRL_CYCCNTENA_Pos*/) |

◆ SCS_BASE

| #define SCS_BASE (0xE000E000UL) |

System Control Space Base Address

◆ SCB_BASE

System Control Block Base Address

◆ SCB

◆ CoreDebug_BASE

| #define CoreDebug_BASE (0xE000EDF0UL) |

◆ CoreDebug

Core Debug configuration struct

◆ DWT